|

Home2L - C/C++ API v1.4-2-g83f4c (2025-08-23)

Smart Tools for a Private Home

|

|

Home2L - C/C++ API v1.4-2-g83f4c (2025-08-23)

Smart Tools for a Private Home

|

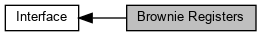

Reference documentation of the Brownie register map.

For Home2L Brownies, the following macros decribe the organization of the virtual registers as accessed by the 'regRead' and 'regWrite' operations.

General ... | |

| #define | BR_REGISTERS 0x40 |

| Number of registers. | |

Notification register(s) ... | |

| #define | BR_REG_CHANGED 0x00 |

| Change indicator register; Reading resets all bits. | |

| #define | BR_CHANGED_CHILD 0x01 |

| – [BR_REG_CHANGED] (hubs only) any child has reported a change | |

| #define | BR_CHANGED_GPIO 0x02 |

| – [BR_REG_CHANGED] any GPIO input changed | |

| #define | BR_CHANGED_MATRIX 0x04 |

| – [BR_REG_CHANGED] any sensor matrix switch changed | |

| #define | BR_CHANGED_ADC 0x40 |

| – [BR_REG_CHANGED] a new ADC sample value exists (only if ADC_PERIOD > 0) | |

| #define | BR_CHANGED_UART 0x08 |

| – [BR_REG_CHANGED] UART status register has changed | |

| #define | BR_CHANGED_SHADES 0x10 |

| – [BR_REG_CHANGED] state of any shades changed (actuator or button, not position) | |

| #define | BR_CHANGED_TEMP 0x20 |

| – [BR_REG_CHANGED] temperature changed (only if configured) (DEPRECATED: may be removed in the future) | |

Registers for GPIO, Timer, Temperature ... | |

| #define | BR_REG_GPIO_0 0x02 |

| GPIOs (0..7): One bit per GPIO. | |

| #define | BR_REG_GPIO_1 0x03 |

| GPIOs (8..15, if present): One bit per GPIO. | |

| #define | BR_REG_TICKS_LO 0x04 |

| Ticks timer (low byte) | |

| #define | BR_REG_TICKS_HI 0x05 |

| Ticks timer (high byte); low byte must be read first, reading low latches high. | |

| #define | BR_REG_TEMP_HI 0x07 |

| Temperature (little endian; reading low latches high). | |

UART registers ... | |

Notes on the UART operation: The RX buffer status value (0..7) indicates how many bytes can be received without error:

The TX buffer status value (0..7) indicates how many bytes can be transferred without error:

| |

| #define | BR_REG_UART_CTRL 0x0c |

| UART control register. | |

| #define | BR_REG_UART_STATUS 0x0d |

| UART status register. | |

| #define | BR_REG_UART_RX 0x0e |

| UART receive register (must be accessed with the "no resend" option) | |

| #define | BR_REG_UART_TX 0x0f |

| UART transfer register (must be accessed with the "no resend" option) | |

| #define | BR_UART_CTRL_RESET_RX 0x01 |

| – [BR_REG_UART_CTRL] Reset RX buffer | |

| #define | BR_UART_CTRL_RESET_TX 0x02 |

| – [BR_REG_UART_CTRL] Reset TX buffer | |

| #define | BR_UART_CTRL_RESET_FLAGS 0x04 |

| – [BR_REG_UART_CTRL] Reset status flags (overflow, error) | |

| #define | BR_UART_STATUS_RX_MASK 0x07 |

| – [BR_REG_UART_STATUS] Mask for RX buffer status values (3 bits, values 0..7) | |

| #define | BR_UART_STATUS_RX_SHIFT 0 |

| – [BR_REG_UART_STATUS] RX buffer status shift | |

| #define | BR_UART_STATUS_TX_MASK 0x38 |

| – [BR_REG_UART_STATUS] Mask for TX buffer status values (3 bits, values 0..7) | |

| #define | BR_UART_STATUS_TX_SHIFT 3 |

| – [BR_REG_UART_STATUS] TX buffer status shift | |

| #define | BR_UART_STATUS_OVERFLOW 0x40 |

| – [BR_REG_UART_STATUS] An RX buffer overflow occured, at least one byte was lost | |

| #define | BR_UART_STATUS_ERROR 0x80 |

| – [BR_REG_UART_STATUS] A receive error (parity or frame) occured; Note: not implemented yet | |

Matrix registers ... | |

Notes on matrix events: Reading removes the oldest entry from the (internal) event queue, the overflow state is not left on read. Writing 0x80 clears the queue and overflow state. The event register allows to detect the precise order of events, which may be used to detect if a window is tilted or closed. This register is not synchronized with any of the raw matrix registers. Initialization/Recovery after overflow or read errors can be done as follows:

The cycle counter is incremented whenever the internal row counter wraps around. It helps to identify whether events have truly happend in the order the events are delivered by the queue. Two events e1 and e2 received in this order with ecycle values of c1/c2 and rows of r1/r2, respectively, are proven to have happened in this order, if (c2 * #rows + r2) - (c1 * #rows + r1) >= #rows If this condition is not met, the real order may be different due to sampling inaccuracies. If this is unwanted, the sampling frequency should be increased (MATRIX_T_PERIOD). | |

| #define | BR_REG_MATRIX_7 0x17 |

| Sensor matrix: raw data (one byte per row, up to 8x8 = 64 bits) | |

| #define | BR_REG_MATRIX_EVENT 0x18 |

| Sensor matrix: Next matrix event. | |

| #define | BR_REG_MATRIX_ECYCLE 0x19 |

| Cycle counter of last read matrix event. | |

| #define | BR_MATRIX_EV_VAL_SHIFT 6 |

| – [BR_REG_MATRIX_EVENT] Bit 6 = value | |

| #define | BR_MATRIX_EV_ROW_SHIFT 3 |

| – [BR_REG_MATRIX_EVENT] Bits 5..3 = row | |

| #define | BR_MATRIX_EV_COL_SHIFT 0 |

| – [BR_REG_MATRIX_EVENT] Bits 2..0 = col | |

| #define | BR_MATRIX_EV_EMPTY 0x80 |

| – [BR_REG_MATRIX_EVENT] Special value: event queue empty | |

| #define | BR_MATRIX_EV_OVERFLOW 0x81 |

| – [BR_REG_MATRIX_EVENT] Special value: overflow | |

Shades registers ... | |

Notes on shades control:

| |

| #define | BR_REG_SHADES_STATUS 0x20 |

| Shades status register. | |

| #define | BR_REG_SHADES_0_POS 0x22 |

| Shades #0: Current position (0..100); 0xff = "unknown". | |

| #define | BR_REG_SHADES_0_RINT 0x23 |

| Shades #0: Internal request (0..100 or 0xff = "none") | |

| #define | BR_REG_SHADES_0_REXT 0x24 |

| Shades #0: External request (0..100 or 0xff = "none") | |

| #define | BR_REG_SHADES_1_POS 0x25 |

| Shades #1: Current position (0..100); 0xff = "unknown". | |

| #define | BR_REG_SHADES_1_RINT 0x26 |

| Shades #1: Internal request (0..100 or 0xff = "none") | |

| #define | BR_REG_SHADES_1_REXT 0x27 |

| Shades #1: External request (0..100 or 0xff = "none") | |

| #define | BR_SHADES_0_ACT_UP 0x01 |

| – [BR_REG_SHADES_STATUS] Shades #0 actor is currently moving up | |

| #define | BR_SHADES_0_ACT_DN 0x02 |

| – [BR_REG_SHADES_STATUS] Shades #0 actor is currently moving down | |

| #define | BR_SHADES_0_BTN_UP 0x04 |

| – [BR_REG_SHADES_STATUS] Shades #0 up button is pushed (= button down after debouncing) | |

| #define | BR_SHADES_0_BTN_DN 0x08 |

| – [BR_REG_SHADES_STATUS] Shades #0 down button is pushed (= button down after debouncing) | |

| #define | BR_SHADES_1_ACT_UP 0x10 |

| – [BR_REG_SHADES_STATUS] Shades #1 actor is currently moving up | |

| #define | BR_SHADES_1_ACT_DN 0x20 |

| – [BR_REG_SHADES_STATUS] Shades #1 actor is currently moving down | |

| #define | BR_SHADES_1_BTN_UP 0x40 |

| – [BR_REG_SHADES_STATUS] Shades #1 up button is pushed (= button down after debouncing) | |

| #define | BR_SHADES_1_BTN_DN 0x80 |

| – [BR_REG_SHADES_STATUS] Shades #1 down button is pushed (= button down after debouncing) | |

System control registers ... | |

| #define | BR_REG_FWBASE 0x3d |

| Firmware base and boot vector location. | |

| #define | BR_REG_CTRL 0x3e |

| Control register. | |

| #define | BR_REG_MAGIC 0x3f |

| Magic value (returns BR_MAGIC after reset) | |

| #define | BR_CTRL_UNLOCK_EEPROM 0x01 |

| – [BR_REG_CTRL] Setting this bit unlocks EEPROM for writing | |

| #define | BR_CTRL_UNLOCK_FLASH 0x02 |

| – [BR_REG_CTRL] Setting this bit unlocks flash memory and SRAM | |

| #define | BR_CTRL_HUB_RESURRECTION 0x04 |

| – [BR_REG_CTRL] Setting this bit puts TWI hub into resurrection mode | |

| #define | BR_CTRL_REBOOT 0xe0 |

| – [BR_REG_CTRL] Writing this value lets the device reboot | |

| #define | BR_CTRL_REBOOT_NEWFW 0xa0 |

| – [BR_REG_CTRL] Writing this value changes the interrupt table according to BR_REG_FWBASE and reboots the device | |

| #define BR_REG_TEMP_HI 0x07 |

Temperature (little endian; reading low latches high).

Bits 12..1 contain the raw temperature value delivered by the TSIC206/306 device. Bit 0 is set if and only if the value ist valid. A value of 0x0000 indicates an unknown temperature.

Definition at line 533 of file interface.h.

| #define BR_REG_FWBASE 0x3d |

Firmware base and boot vector location.

This is the base address of the active firmware in units of BR_FLASH_PAGESIZE bytes (64/0x40 on ATtiny84, ATtiny861). Writing to this register followed by writing BR_CTRL_REBOOT_NEWFW to BR_REG_CTRL causes the interrupt table to be rewritten and the CPU reset. This register is initialized with the actual firmware base; reading it allows to locate the running firmware.

Definition at line 724 of file interface.h.